### **Dynamic Characterization Platform**

The Dynamic Characterization Platform from Littelfuse is designed to:

- Measure

- MOSFET switching losses, switching times, and gate charge accurately.

- Schottky Barrier Diode (SBD) and body diode reverse recovery accurately.

- Provide an informed reference design for gate drive and power loop PCB layout.

- Provide informed recommendations for gate drive layout and components.

- Promote streamlined device validation and quicker design cycles.

The Dynamic Characterization Platform (DCP) enables design engineers to characterize the high performance silicon carbide (SiC) MOSFETs and diodes offered by Littelfuse with high accuracy. Functionality highlights of this evaluation kit include:

- Designed for TO-247-3L SiC MOSFETs and TO-220-2L SiC Schottky Barrier Diodes

- Power loop and gate drive circuitry optimized for ultra-fast dV/dt and dl/dt events

- Integrated input signal and measurement probe interface connections

For more information about this evaluation kit, including design files, please visit our SiC products web page at: <a href="http://www.littelfuse.com/products/power-semiconductors/silicon-carbide.aspx">http://www.littelfuse.com/products/power-semiconductors/silicon-carbide.aspx</a>.

#### Contact Information:

- For further details about procuring the Dynamic Characterization Platform hardware, please contact a Littelfuse Business Development Manager:

- Europe, Michael Ketterer, mketerer@littelfuse.com

- China/Taiwan, Teddy To, tto@littelfuse.com

- Americas/Japan, Koichiro Yoshimoto, kyoshimoto@littelfuse.com

- India, Navneet Vinaik, nvinaik@littelfuse.com

- For further technical details about the Dynamic Characterization Platform, please contact our SiC Application Support Hotline, powersemisupport@littelfuse.com

#### Introduction

High voltage silicon carbide MOSFETs and diodes have fast switching speeds and very low switching losses. This enables power converters to be operated at higher frequencies when compared to traditional power converters that use silicon devices. Higher operating frequencies and very low switching and conduction losses lead to multiple system-level optimization opportunities, including power converters with higher efficiency and power density. Reduction in magnetics size and simpler thermal management designs can also lead to total system cost reduction. Although previous generations of power converters were limited by the switching speed and high losses of high voltage silicon switches, new fast switching and low loss SiC MOSFETs and diodes all but eliminate this constraint and provide designers with the opportunity to redesign compact, superefficient power converters with low cost.

Although SiC MOSFETs behave much like silicon MOSFETs and are quite simple to drive, designers must pay special attention to certain aspects in order to harness the full advantage of these fast switching devices. The switching behavior of the MOSFETs can be severely impaired by parasitic inductances stemming from poor PCB layouts. These parasitic inductances, coupled with the fast dV/dt and dl/dt characteristics of the SiC MOSFETs, can lead to a number of undesirable effects, including voltage and current overshoot, increased switching losses, and system instability. Additionally, using traditional silicon IGBT based techniques to characterize the switching behavior of SiC MOSFETs may result in erroneous conclusions about switching losses due to insufficient measurement probe bandwidth, equipment inadequacy, etc.

The Dynamic Characterization Platform (DCP) from Littelfuse is designed to characterize SiC MOSFET and diode switching losses via the double-pulse technique. It can also be used to characterize other typical dynamic parameters provided in MOSFET and diode datasheets, such as switching times, gate charge, and reverse recovery. As previously mentioned, measuring these parameters for SiC devices requires an optimized board layout and precise voltage/current sensing techniques. To begin implementing good SiC device characterization practices, please visit our website and download the DCP reference design package, which contains schematic, board layout, and Bill of Materials files, along with this application note.

| Electrical Specifications  |               |                |       |

|----------------------------|---------------|----------------|-------|

| Parameter                  | Typical Value | Maximum Rating | Units |

| Input DC Link Voltage      | 800           | 1000           | V     |

| Input Control Voltage      | 12            | 13.2           | V     |

| Output Peak Current        | -             | 100            | А     |

| <b>Ambient Temperature</b> | -             | 55             | °C    |

| Gate Driving Voltage       | +20/-5        | +22/-6         | V     |

#### Overview

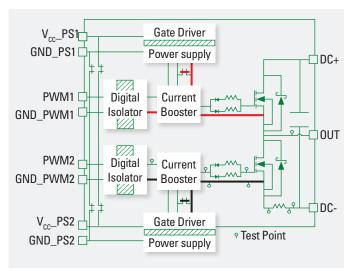

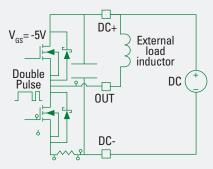

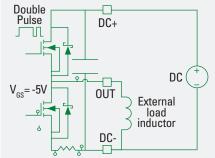

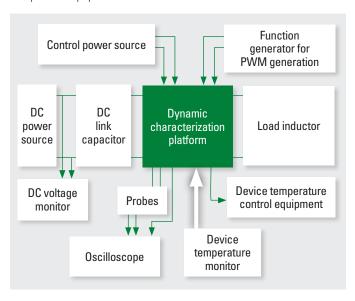

Figure 1 is a block diagram of the Dynamic Characterization Platform. It is arranged in a single-phase leg configuration that accommodates two SiC MOSFETs and optional anti-parallel Schottky diodes. Each MOSFET has its own gate driver circuit, including individual digital isolators, current boosters, and isolated power supplies.

Figure 1: Block diagram of the Dynamic Characterization Platform

The DCP includes three high-voltage power connections (DC+\_Con2, DC-\_Con1 and OUT\_Con3), two pairs of low-voltage connections for gate driver control circuitry ( $V_{\rm cc}$ \_PS1/GND\_PS1 and  $V_{\rm cc}$ \_PS2/GND\_PS2), two BNC terminals for gate signals (PWM1/GND\_PWM1 and PWM2/GND\_PWM2), and one 8-pin header that can be used as an alternative interface for the gate signals (not shown in Figure 1).

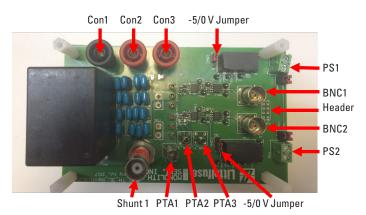

Figure 2: Interface Connections for Dynamic Characterization Platform

Each switch position's gate driver circuitry features a Silicon Labs digital isolator [Si8261], an IXYS current booster [IXDN614], and a Murata 2W isolated DC-DC converter [MGJ2D122005SC]. The Murata DC-DC converter uses a +12 V input to generate +20 V and -5 V rails with a 5.2 kV DC isolation barrier. The negative driving voltage can be configured (-5 V or 0 V) via a 100-mil header jumper. The gate loop is separated into two (diode + 0603 SMD resistor) legs to allow for different turn-on and turnoff gate resistances. The on-board probe-tip adapters (PTAs) improve measurement accuracy for gate-source voltage (V<sub>cs</sub>) and drain-source voltage (V<sub>DS</sub>). A coaxial current viewing resistor shunt is used for accurate switching current measurement. High-voltage DC link capacitors are provided in the form of one larger film capacitor (which stabilizes the DC bus during switching transients) in parallel with multiple smaller ceramic capacitors (which provide a decoupling function for current commutation between devices). A phase leg configuration that includes accommodations for two SiC MOSFETs and optional anti-parallel Schottky diodes supports testing either MOSFETs or diodes. The socket mounting method for the MOSFETs and diodes allows for fast and easy swapping of DUTs. Likewise, high-voltage banana connectors are used for convenient power connections. An on-board through-hole resistor can be mounted for resistive load testing; an external load inductor is needed for inductive load pulse testing.

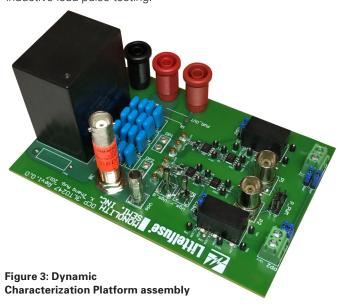

The dimensions of the DCP board (Figure 3) are 132 mm x 86 mm. It is designed to perform pulse testing only, so no device cooling accommodations are provided. This board is designed to test MOSFETs in 3-lead TO-247 packages and diodes in 2-lead TO-220 packages. Custom DCPs for other through-hole packages and SMD packages can be developed on request.

#### Resistive load test:

- Single-pulse test

- Test switching behavior of switching MOSFET with resistive load (delay time, rise/fall time)

- Resistive load implemented via onboard through-hole resistor

### CIL MOSFET switching loss test:

- Double-pulse test

- Test switching behavior of switching MOSFET with inductive load

- Test gate charge behavior of MOSFET

- Selective MOSFET or diode for freewheeling device

- Inductive load implemented via off-board load inductor

#### Reverse recovery test:

- Double-pulse test

- Test reverse recovery behavior of freewheeling devices

- Selective MOSFET or diode for freewheeling device

- External load inductor needed

Table 1: Possible configurations for Dynamic Characterization Platform

### **Configurations**

The DCP has the flexibility to implement several important SiC device characterization test circuits, including resistive load single-pulse testing for switching time behavior, inductive load double-pulse testing for switching energy/time behavior and gate charge behavior, and inductive load double-pulse testing for reverse recovery behavior.

Table 1 summarizes the possible topologies f or different tests. Switching tests can be performed with or without anti-parallel SBDs. The free-wheeling device can be implemented via a single SBD, a single MOSFET (with body diode), or a combination of an SBD and a MOSFET in parallel with one another as shown in the schematics in Table 1.

#### **Hardware Description**

**Key Components and Connectors**

#### **Device under test (DUT)**

This Dynamic Characterization Platform can characterize the switching behavior of the switching devices and the free-wheeling devices in a half-bridge configuration. For switching device characterization, the DUT can be implemented as a MOSFET only or as a MOSFET with an external anti-parallel diode. For free-wheeling device characterization, the DUT can be implemented as a single free-wheeling diode, a MOSFET with body diode, or a MOSFET with body diode and an additional free-wheeling diode in parallel.

#### DC link capacitor and decoupling capacitor

Decoupling capacitors provide energy during device switching. DC link capacitors stabilize DC link voltage during switching transients. The decoupling capacitors and DC link capacitor in the DCP together form a low-pass filter that filters the switching current on the DC bus. This reduces the impact of any parasitic inductance related to the wire connection between the DC source and the on-board DC bus of the test system.

#### Free-wheeling device

When the bottom switch position MOSFET is turned off in a double-pulse test, a current path is required for the energy stored in the off-board inductor to circulate through. This is accomplished by inserting a semiconductor element that limits current flow to one direction in parallel with the inductor. The semiconductor element is commonly composed of a SiC SBD, SiC MOSFET with body diode, or a SiC MOSFET and SiC SBD in parallel. These configurations represent common, real-world configurations seen in a buck or boost converter with an SiC SBD diode for the free-wheeling device. Another common

configuration appears in a half-bridge topology, where the need for a free-wheeling device is satisfied by the body diode of the SiC MOSFET.

#### Isolated power supply

Implemented in the gate driver circuitry, this component provides an isolation barrier for logic signals.

#### Current viewing shunt resistor (R<sub>shunt</sub>)

A coaxial type shunt resistor offers the optimal solution for measuring the device current. The coaxial shunt allows making a high bandwidth measurement while introducing only a minimal amount of parasitic inductance into the power loop of the testing circuit. For details of the coaxial shunt, refer to T&M Research® (SSDN-414 series,  $50~\text{m}\Omega$  with 2000 MHz bandpass frequency and 0.18~ns rise time). The output of the CVR is directly connected to the oscilloscope via a  $50~\Omega$  terminator and an RG58 BNC cable.

#### Voltage measurement probes

Passive probes are recommended for drain-source voltage and gate-source voltage measurements. High bandwidth, low input impedance, and proper de-skewing between voltage and current measurements are necessary for accurate switching loss measurements. Probe-tip adapters are provided for convenient PCB to probe-tip interface connections and optimized voltage measurement.

#### Off-board load inductor

Here are some important tips for selecting a proper off-board inductor:

- Avoid saturation at target device current.

- Ensure enough inductance so that the turn-off and turn-on events will have similar current.

- Larger inductance will allow for easier and more accurate programming of device current.

- Avoid paralleling of multiple inductors, which would result in higher equivalent parallel capacitance and potential for LC resonant ringing during a switching event.

#### Signal and power connection

Input PWM signals should be controlled with a 3.3 V signal via BNC1 and BNC2. Gate drive power supply input voltage should be 12 V, applied via PS1 and PS2.

#### **Connector definitions**

The board (Figure 3) has three power connections: Con1 is for negative DC bus input, Con2 is for positive DC bus input, and Con3 is the mid-point of the phase leg. PS1 and PS2 are for the +12 V power supply input for the gate driver control circuitry. BNC1 and BNC2 are gate signal input connection terminals for the function generator. The Header connector provides an alternative gate signal input option for digital controllers. The definition of the Header connector is shown in Table 2.

| Pin | Definition |  |

|-----|------------|--|

| 1   | PWM1       |  |

| 2   | GND_PWM1   |  |

| 3   | NC         |  |

| 4   | NC         |  |

| 5   | NC         |  |

| 6   | NC         |  |

| 7   | PWM2       |  |

| 8   | GND_PWM2   |  |

Table 2: Header connector pin definitions

For measurements, three probe-tip adapters (PTAs) are implemented with measurement loop reduction in mind. PTA1 is for the drain-source voltage ( $V_{DS}$ ) measurement. PTA2 is for the gate-source voltage ( $V_{GS}$ ) measurement. PTA3 is for the measurement of the gate signal before gate resistor (used during gate charge measurement tests). Shunt1 is the BNC connection for the switching current ( $I_{DS}$ ) measurement.

#### Gate drive loop and power loop design

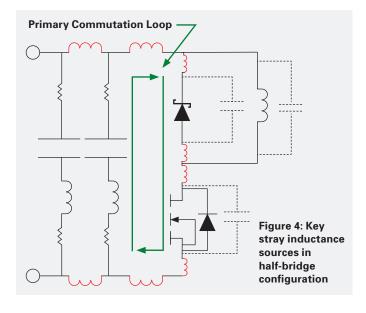

SiC devices switch extremely fast, so it is important to minimize the voltage overshoot and current ringing during switching transients. A common contributor to ringing seen during switching events is the loop inductance in the semiconductor

packaging and PCB layout design. Figure 4 shows some key sources of parasitic inductances in a half-bridge configuration.

The DCP uses design approaches that optimize both power loop and gate loop design to minimize loop inductance and cross coupling. Here are some of these design guidelines:

- The current booster should be placed as near as possible to the gate pin of the SiC MOSFET to reduce the length of the gate path. The source pin of the MOSFET should be connected to a copper ground plane on the PCB directly beneath the gate path. This results in the gate loop being minimized in such a way that only the thickness of the PCB contributes to the gate loop size.

- Additional decoupling capacitors for the current booster ICs are recommended. These decoupling capacitors should also be placed as near as possible to the gate of the MOSFET to reduce the gate loop.

- DC link decoupling capacitors are necessary to reduce the drain-source voltage ringing during switching. Multiple small decoupling capacitors in parallel are recommended to reduce parasitic inductance of each capacitor. The decoupling capacitors should also be placed as near to the SiC MOSFETs as possible.

- A laminated DC bus structure is recommended to reduce DC bus inductance. For that reason, it is better to use copper planes than traces for the DC positive and DC negative bus signals. Furthermore, these planes should reside on different PCB layers and overlap with each other to form the laminated DC bus structure.

- The placement of the two MOSFETs and their antiparallel diodes should be carefully considered to ensure a small current commutation loop between the top device and bottom device.

#### Load inductor selection

To collect accurate switching loss measurements, the load inductor must be chosen carefully. The load inductor should have low equivalent parallel capacitance (EPC) compared to the output capacitance of the DUT. Selecting a load inductor that has an EPC smaller than 10 pF is recommended when testing 1200 V, 80 m $\Omega$  SiC MOSFETs from Littelfuse. Another important quality of the load inductor is that it should not be saturated at the target turn-off/turn-on current. For internal testing

purposes, Littelfuse leverages four high current encapsulated inductors [EK55246-341M-40AH] from Coil Winding Specialist, Inc. These have been custom packaged in enclosures with banana jack interface terminals that allow for quick and easy configuration depending on testing needs (e.g., low current + high inductance or high current + low inductance operation).

Figure 5: Load inductor example

### **Example Application and Measurement Test setup**

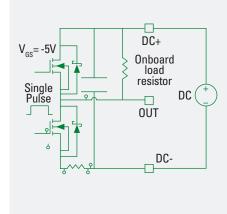

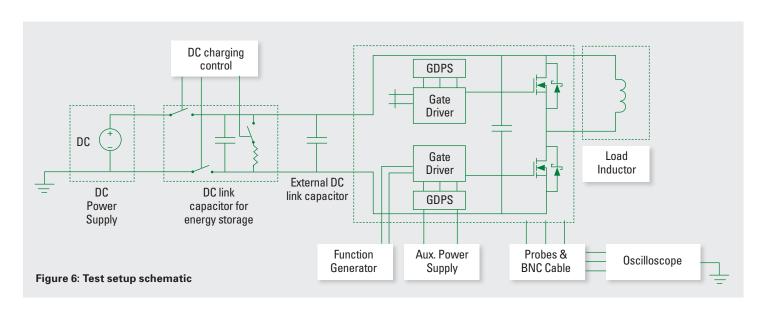

Figure 6 shows the block diagram schematic of a double-pulse test setup. In this test, an inductive load is placed in parallel with a free-wheeling diode (FWD) in the upper switch position. These elements make up the free-wheeling path for current during DUT turn-off states. The DUT occupies the lower switch position. This testing configuration is used to study switching energy and gate charge characteristics of the DUT.

Note: The measurement equipment and the DC power supply each have their own connection to earth ground. To prevent a ground loop that may cause significant measurement error, isolating the DCP galvanically from the DC power supply during tests is recommended while measurements are being collected. In this test system, voltage controlled relays [P105] from GIGAVAC are used for disconnecting the DC power supply (positive and negative rails) from the DCP. The DC link capacitance is sized so that it can maintain the desired bus voltage throughout the test after being disconnected from the DC power supply. This improves measurement conditions by minimizing the risk of ringing during transient events caused by ground loops. If the system does not have accommodations for a sufficiently sized DC link capacitor that allows for disconnection from the DC voltage supply as described above, the system still requires, at minimum, a DC link capacitance of sufficient size to maintain DC voltage during device switching. Refer to the appendix for additional details regarding required peripheral equipment.

#### Measurement details

The high switching speed of SiC MOSFETs means the dv/dt and di/dt may exceed 80 V/ns and 5 A/ns respectively under certain test conditions. These devices are switching on and off within tens of nanoseconds. Therefore, it is critical that the measurement probes have adequate bandwidth, good dynamic performance, and very small loading capacitance. For testing with the DCP, passive voltage probes are recommended for  $V_{\rm DS}$  and  $V_{\rm GS}$  measurements. A current viewing resistor shunt is recommended for the  $I_{\rm DS}$  measurement.

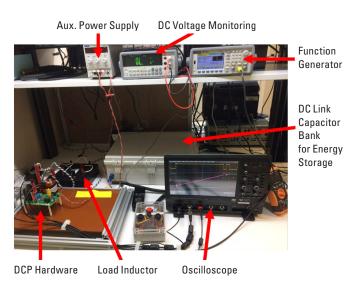

Figure 7: Test setup

For this example, a current viewing resistor (CVR) from T&M Research (SSDN-414-05) is used to measure  $I_{\rm DS}.$  This model's specifications include a 2 GHz bandwidth and 0.18 ns rise time. The output of the CVR is directly connected to the oscilloscope via a 50  $\Omega$  terminator and an RG58 BNC cable. Note: The settings for the oscilloscope's channel used for this measurement should be configured to reflect a 50  $\Omega$  termination.

For the V<sub>DS</sub> measurement, a probe-tip adapter is provided on the DCP PCB that accommodates the 400 MHz bandwidth, high-voltage passive probe [PPE4KV] from Lecroy. For the V<sub>GS</sub> measurement, a probe-tip adapter is provided on the DCP PCB that accommodates the 500 MHz bandwidth, low-voltage passive probe [PPE023] from Lecroy. If other voltage probes are used, the user should ensure that the probes have  $\geq$ 400 MHz bandwidth and sufficient voltage margin for the signal to be measured. If the probe-tip adapter does not match with the probe in use, the user has the option to replace the probe-tip adapter with an SMA connector and an SMA to probe-tip adapter.

(a) Double-Pulse Test captured waveforms (10 µsec/div)

Figure 8: Probe-tip to PCB interface connections

In addition to adequate probes, a high-performance oscilloscope should also be used to ensure accurate voltage and current measurements. The minimum recommended specifications for the oscilloscope are: Bandwidth  $\geq$  400 MHz and Sample rate  $\geq$  2.5 GS/s.

#### **Test results**

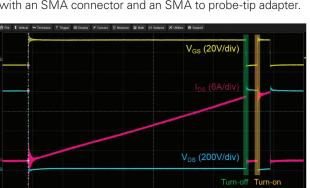

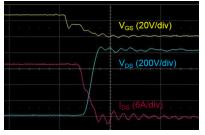

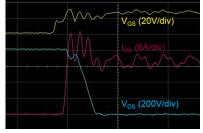

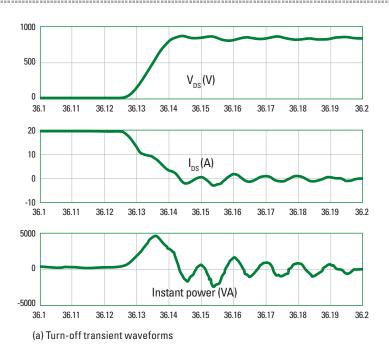

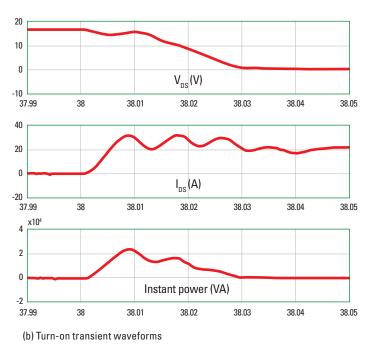

Figure 9 presents results for a test performed with an 800 V DC bus voltage and a device current of 20 A. In this figure, the gate-source voltage ( $V_{\rm GS}$ ), drain-source voltage ( $V_{\rm DS}$ ), and device current ( $I_{\rm DS}$ ) are shown. Sub figures (b) and (c) show magnified portions of the waveforms from (a) that correspond to the turn-off (b) and turn-on (c) events. These events are used to characterize the switching behavior of the MOSFET in detail by describing its switching energy, switching speed, rise and fall times, voltage overshoot, etc.

(b) Turn-off transient waveforms (50 nsec/div)

(c) Turn-on transient waveforms (50 nsec/div)

Figure 9: Oscilloscope screen captures of double-pulse test waveforms

#### Post processing of test data

To obtain numerical values for the devices' switching characteristics, a certain amount of post processing must be done. MATLAB® is a useful software tool for handling these heavy computational load calculations. After importing the raw data into the post-processing environment, the next step is to ensure the drain-source voltage ( $V_{DS}$ ) and device current ( $I_{DS}$ ) are properly de-skewed. The switching loss results are highly sensitive to this step, so it is critical to the process; otherwise, results may be skewed by a significant percentage.

There are two ways to ensure the channels are properly deskewed. The first way, a hardware de-skew, is performed by connecting the two channels used to measure the  $V_{\rm ps}$  and  $I_{\rm ps}$ signals to the same voltage signal/reference on the oscilloscope and adjusting the channel delay settings accordingly until the waveforms align with each other. Note: The connections from the oscilloscope channels to the oscilloscope voltage signal/ reference should be made with the probes (HV voltage probe for  $V_{DS}$  and BNC cable for  $I_{DS}$ ) that will be used in the tests to ensure proper compensation. This method should always be the first step to ensuring proper de-skewing of the oscilloscope channels. A software de-skew can be performed as a way to check the accuracy of this hardware de-skew. This method involves first plotting the  $V_{\rm DS}$  and  $I_{\rm DS}$  current waveforms, both with respect to time. During the turn-off event, the  $V_{\rm DS}$  signal should first cross the DC bus voltage set point (e.g., 800 V in this example) at the same time as the device current first crosses 0 A. If these instances occur at the same time, the hardware de-skew was successful and no further action is necessary. If the events occur at slightly different times, a manual shift of one waveform  $(V_{DS} \text{ or } I_{DS})$  along the time axis can be performed to align the two events previously discussed.

Figure 10 presents an example of plots generated with MATLAB for the turn-on and turn-off transient voltage ( $V_{DS}$ ), current ( $I_{DS}$ ), and instantaneous power after a proper oscilloscope channel deskew. From these waveforms, switching energy calculations and switching behavior of the DUT can be derived.

The waveforms shown in Figure 10 indicate that, during the turn-off event, a voltage overshoot of ~70 V is present, dv/dt = 68.72 V/ns, di/dt = 1 A/ns, and turn-off loss is ~60  $\mu$ J; during the turn-on event: a current overshoot of ~10 A is present, dv/dt = 39.47 V/ns, di/dt = 5.2 A/ns, and turn-on loss is ~270  $\mu$ J. Note: switching loss values are obtained via integration of instantaneous power.

Figure 10: MATLAB processing of double-pulse test waveforms

#### **Sources for Further Information**

B. Ozpineci, et al., "Characterization of SiC Schottky diodes at different temperatures," in *IEEE Power Electronics Letters*, vol. 1, no. 2, pp. 54-57, June 2003.

C. New, A. N. Lemmon and A. Shahabi, "Comparison of methods for current measurement in WBG systems," 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, 2017, pp. 87-92.

Littelfuse, Inc. LSIC2SD120A10 1200 V, 10A SiC MOSFET datasheet. 2017.

Littelfuse Inc. LSIC1MO120E0080 1200 V, 80 m $\Omega$  SiC MOSFET datasheet. 2017.

X. Zhang, L. Gant, G. Sheh and S. Banerjee, "Characterization and Optimization of SiC Freewheeling Diode for Switching Losses Minimization Over Wide Temperature Range," *PCIM Europe 2017*; Germany, 2017, pp. 1-7.

Z. Zhang, B. Guo, F. F. Wang, E. A. Jones, L. M. Tolbert and B. J. Blalock, "Methodology for Wide Band-Gap Device Dynamic Characterization," in *IEEE Transactions on Power Electronics*, vol. 32, no. 12, pp. 9307-9318, Dec. 2017.

#### **Appendix**

Peripheral equipment

#### **Design Files**

For detailed PCB schematic and layout files, please visit: <a href="http://www.littelfuse.com/products/power-semiconductors/silicon-carbide.aspx">http://www.littelfuse.com/products/power-semiconductors/silicon-carbide.aspx</a>.

#### **Disclaimer**

Note: This evaluation kit is not designed to meet any safety standards or regulatory guidelines. It is intended to be used by experienced engineers or equally trained professionals in a lab setting only. Littelfuse assumes no responsibility for death, injury, or damaged equipment resulting from improper use of this evaluation kit.

Littelfuse products are not designed for, and shall not be used for, any purpose (including, without limitation, automotive, military, aerospace, medical, life-saving, life-sustaining or nuclear facility applications, devices intended for surgical implant into the body, or any other application in which the failure or lack of desired operation of the product may result in personal injury, death, or property damage) other than those expressly set forth in applicable Littelfuse product documentation. Warranties granted by Littelfuse shall be deemed void for products used for any purpose not expressly set forth in applicable Littelfuse documentation. Littelfuse shall not be liable for any claims or damages arising out of products used in applications not expressly intended by Littelfuse as set forth in applicable Littelfuse documentation. The sale and use of Littelfuse products is subject to Littelfuse Terms and Conditions of Sale, unless otherwise agreed by Littelfuse.

Littelfuse, Inc.

8755 West Higgins Road, Suite 500 Chicago, IL 60631 USA Phone: (773) 628-1000

Littelfuse.com